文章图片

本文由半导体产业纵横(ID:ICVIEWS)综合

最尖端逻辑制程从“三足鼎立”走向“四厂争霸” , 再进一步 。

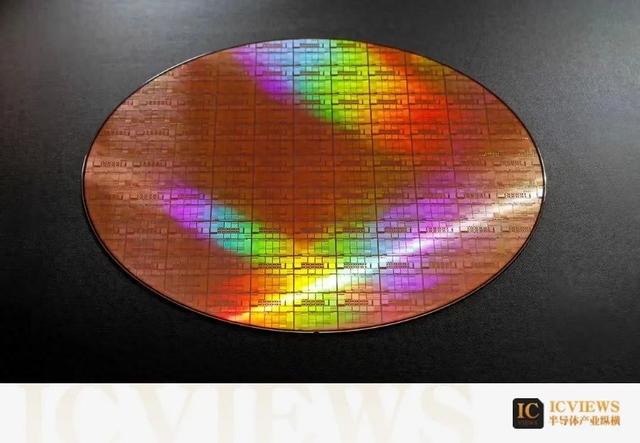

日本半导体制造商Rapidus宣布启动2nm GAA晶体管的试制 , 并展示了其首块2nm GAA晶圆 。 这也是最尖端逻辑制程从“三足鼎立”走向“四厂争霸”道路上的关键里程碑 。

去年12月 ,Rapidus在SEMICON Japen 2024上 , 展示了其与IBM合作在美国纽约州奥尔巴尼纳米技术综合体制造的 2nm GAA晶体管原型晶圆 。 今年2月 , Rapidus社长小池淳义透露 , 公司计划在2025年4月1日启动2nm GAA制程试产 , 并于2025年6月向博通交付2nm芯片样品 , 2027年在IIM-1开始量产2nm产品 。

IIM-1是Rapidus位于北海道千岁市的2nm芯片工厂 , 2023年9月破土动工 。 2024年12月 , Rapidus接收首台ASML EUV光刻机(重达71 吨) , 并完成四阶段安装 , 成为日本首家拥有量产用EUV设备的公司 。 同月 , Rapidus会长东哲郎在SEMICON Japan 2024展会上宣布 , EUV 光刻设备于当月开始交付 , 200余台设备计划在2025年3月底前全部到位 。 2025年3月底 , IIM-1晶圆厂完成全部设备安装 , 包括ASML EUV和DUV光刻系统 , 具备试生产条件 。

值得一提的是 , Rapidus选择直接从40nm跳跃至2nm , 这种跨越在半导体史上绝无仅有 。 技术来源依托三大支柱:与IBM合作获得2nm技术基?。 涣媳壤盜MEC获取EUV光刻技术佳能、铠侠开发的纳米压印技术作为“秘密武器” 。

当制程升级至2nm时 , 晶体管结构从多年来一直使用的FinFET(鳍式场效应晶体管)转变为GAAFET(全环绕栅极场效应晶体管) 。 这给制程迭代带来了新的挑战:如何实现多阈值电压以使芯片在较低电压下执行复杂计算 。

由于2nm名义制程下N型和P型半导体通道之间的距离相当狭窄 , 需要精确的光刻才能实现多阈值电压 , 并且不会对半导体性能产生巨大影响 。 然而 , IBM和Rapidus引入了两种不同的选择性减少层(SLR)芯片构建工艺 , 成功地达到了目标效果 。

IBM研究院高级技术人员Bao Ruqiang表示:“与上一代FinFET相比 , Nanosheet纳米片的结构非常不同 , 而且可能更复杂 。 我们提出的新生产工艺比以前使用的方法更简单 , 我们认为这将使我们的合作伙伴Rapidus更容易、更可靠地大规模使用2nm片技术来制造芯片 。 ”

在市场定位上 , 东哲郎明确表示不会与台积电正面竞争大规模标准品 , 而是聚焦专用芯片市场 , 瞄准机器人、自动驾驶和远程医疗等新兴领域 。 2025年6月 , Rapidus宣布将基于西门子Calibre平台开发专用设计套件 , 实现制造与设计的协同优化(MFD) 。 Rapidus 社长小池淳义指出 , 通过与西门子的合作 , Rapidus 将推进制造和设计的协同优化 , 实现设计制造协同优化(DMCO)概念 , 大幅缩短2nm工艺的流片时间 , 为客户提供更高效的服务 。

在客户拓展方面 , 除博通外 , NVIDIA CEO黄仁勋在2024年11月暗示可能考虑Rapidus代工AI芯片 。 例外 , 日本AI企业Preferred Networks和Sakura Internet也将成为其客户 。

*声明:本文系原作者创作 。 文章内容系其个人观点 , 我方转载仅为分享与讨论 , 不代表我方赞成或认同 , 如有异议 , 请联系后台 。

【日本首块2nm晶圆,亮相】想要获取半导体产业的前沿洞见、技术速递、趋势解析 , 关注我们!

推荐阅读

- 30亿元/台!全球首台顶级光刻机出货 支持后2nm工艺:中国厂商不可能买到

- 台积电、英特尔、三星2nm工艺良率披露,最高65%

- Intel Nova Lake-S已投片:台积电2nm工艺,最多52核心

- 三星计划年底前将2nm良率提升至70%!

- 2nm版本高通骁龙8 Elite 2曝光

- 三星6月内将2nm良率提升至70%

- 三星2nm版骁龙8 Elite 2来了?搭载机型待定

- 超越苹果发哥!骁龙8Elite2喜提2nm工艺,但不是台积电代工

- 高通SM8850s被确认:直入2nm时代,明年登场!

- 手机或要贵1000块?2nm芯片,手机厂商用不起了