文章图片

文章图片

众所周知 , 目前在芯片的生产环节 , 主要由三个部分组成 , 分别是设计、制造、封测 。

这三个环节是相互独立 , 又相互依存的 , 同时遵循木桶理论 , 那就是其整体水平 , 其实是取决于最弱的那一环节的 。

举个例子 , 能设计7nm芯片 , 但制造在10nm , 封测在5nm , 那么最终水平就是10nm , 取决于最差的那个环节 。

事实上 , 也正是如此 , 目前对于中国大陆而言 , 真正卡脖子的 , 其实是制造这一块 , 因为制造远远的落后于设计、封测了 。

先说设计这一块 , 小米已经设计出了3nm的芯片 , 但由于国内制造水平跟不上 , 所以小米的3nm芯片是委托给台积电代工的 , 采用的是台积电的第二代3nm工艺 。

从性能来看 , 小米的这颗芯片 , 已经可以比肩苹果的A18芯片 , 高通的骁龙8Gen3芯片 , 可见在设计这一块 , 我们确实达到了3nm的水平 。

封测就不用说了 , 早在2022年的时候 , 国内的封测企业就已经能够封测3nm的芯片了 , 并且已经有国外的客户 , 将3nm的芯片交给国内的企业封测 。

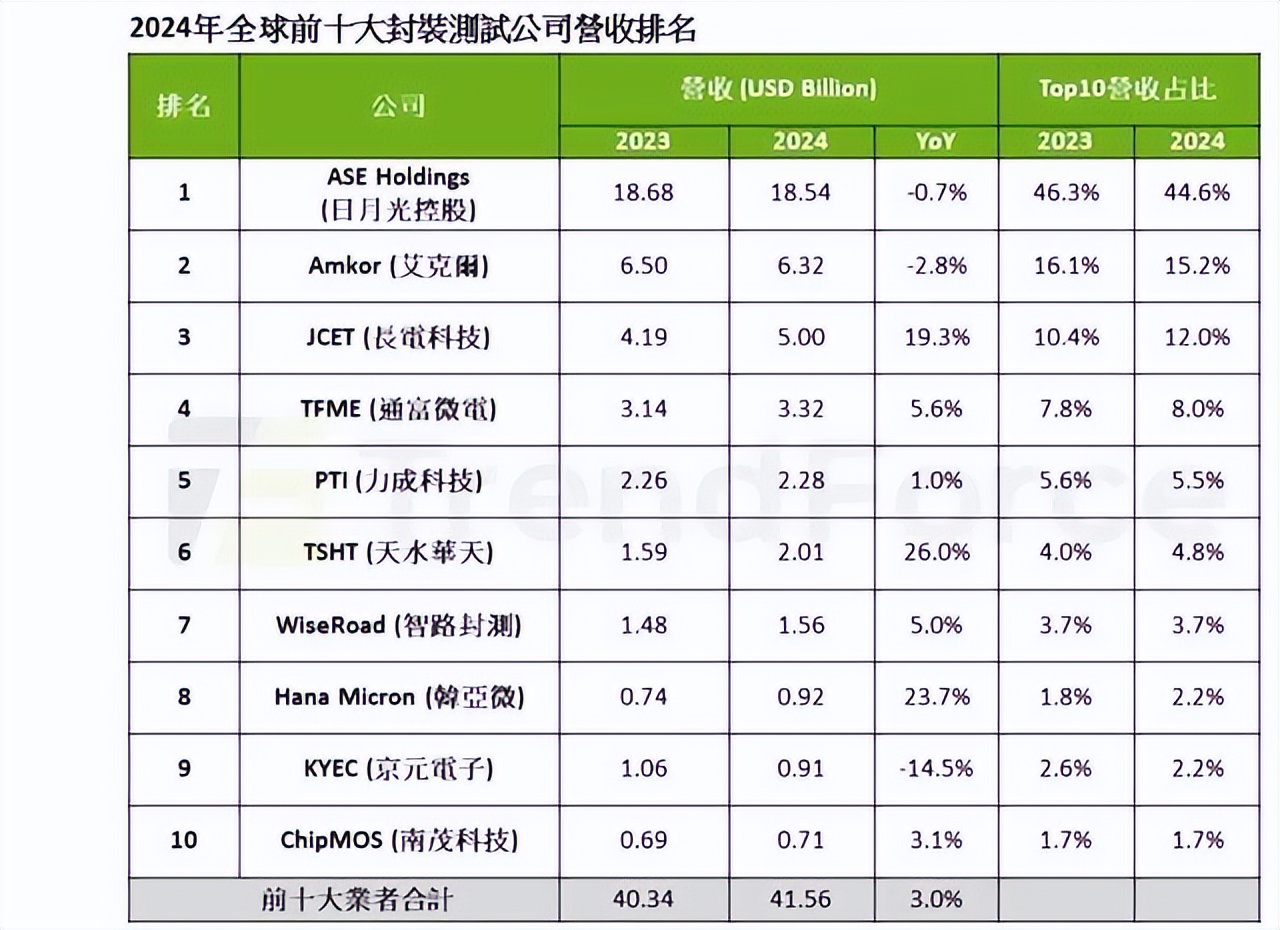

毕竟中国芯片封测水平可是第一梯队的 , 全球前10大封测企业中 , 中国大陆有4家上榜 , 在全球市场拿下了30%左右的份额 , 是相当厉害的 。

而制造这一块 , 相比于设计、封测确实是落后很多 。

中芯国际已经是中国大陆最厉害的芯片代工制造企业了 , 之前对外公开的是14nmFinFET工艺 , 后来虽然不再公布 , 而媒体据称有N+1、N+2 , 但据报道 , 目前的水平大约也是等效于7nm的水平 , 突破等效5nm都有困难 。

【我们能设计、封测3nm芯片,但制造拖后腿,压力给到中芯国际了】可见 , 制造是目前我们最大的短板 , 因为制造跟不上来 , 所以很多企业能够设计3nm芯片 , 但却制造不了 , 比如海思 。

为什么制造会更难一些 , 因为制造需要大量的设备、材料等 , 这些设备材料都是被限制的 , 最典型的就是EUV光刻机 , 它是制造7nm以下芯片必须用到的设备 , 美国不准ASML卖给我们 。

所以说 , 我们的芯片制造需要加油了 , 现在的压力给到了中芯国际了 , 只要制造能够和设计同频 , 达到3nm水平 , 那么中国芯就啥也不怕了 。

当然 , 中芯国际的压力又会传导至国产设备厂商那里 , 只有设备突破 , 然后中芯国际才能突破 , 所以接下来 , 需要整个供应链一起突破 。

推荐阅读

- AI/AR技术持续占据主战场,五大巨头加大投入打响智能眼镜持久战

- 光刻机有后门吗:ASML能否远程关闭

- 多模态扩散模型开始爆发,这次是高速可控还能学习推理的LaViDa

- 国产Top5厂商开始发力:四摄设计+外挂镜头,手机影像迎来新时代!

- 不想手机都千篇一律?代价可能会非常大

- 智能体大潮汹涌,但留给天工和阶跃们的时间不多了

- “homeOS”商标曝光,苹果智能家居重整旗鼓

- 谷歌推出新功能,密码不安全Chrome自动帮忙改

- 鑫谷数智DM-850G电源评测超金牌智能“小金刚”

- 消息称小米荣耀传音的智能手机一季度在拉美出货1060万部 不及去年同期