文章图片

文章图片

文章图片

文章图片

本文由半导体产业纵横(ID:ICVIEWS)编译自Semiconductor Engineering

为保障良率 , I/O 测试和备用 lane 替换修复将更普遍 。

如今 , 高性能计算设备中集成了数万个互连 , 为实现足够的良率 , Chiplet 接口的冗余设计已成为必要 。 随着这些互连数量和密度的增加 , 良率前景只会愈发黯淡 。

二十多年来 , 高速 I/O 接口一直包含管理现场系统板故障的可靠性策略 。 例如 , 2007 年推出的 PCI Express 2.0 标准包含 16 条事务 lane 。 但如果某条 lane 发生故障 , 只会使用其中 8 条 , 将使事务处理速率减半 。 这种通常被称为 “优雅降级” 的策略 , 至今仍是 UCIe 等计算 Chiplet 接口所采用的策略 。

但如今 , HBM 和 UCIe 接口包含了多芯片组件中单 lane 故障的应急措施 , 规定了备用 lane 以替换 Chiplet 之间出现故障的信号互连 。 一旦检测到故障 lane , 就会用备用 lane 进行替换 , 从而 “修复” 故障 lane 。 工程团队可以在整个测试制造流程中更换有问题的 lane 。 这种能力还可用于客户系统 , 以应对与组装相关的可靠性和磨损故障机制 。

尽管如此 , 随着先进的组装工艺促成了高密度的 2.5D 和 3D 架构 , 基于 Chiplet 的系统中的信号互连数量将攀升至数十万 , 将对制造和系统级可靠性的 I/O 测试及修复策略构成挑战 。 因此 , 测试内容需要全面检测与 I/O 相关的故障 。

“对于高容量、高数据速率的互连 lane , 设计人员需要考虑可能因交叉耦合和其他缺陷类型而显现的各种故障 , ” 新思科技(Synopsys)多芯片测试相关 SLM 产品的首席产品经理费萨尔?戈里亚瓦拉(Faisal Goriawalla)表示 , “基于一套全面的算法测试图形 , 如果发现任何 lane 存在缺陷 , 就必须有一套机制通过用良好的 lane 替换有问题的 lane 来进行 lane 修复 。 ”

其优势在于 , 追踪故障发生的位置和时间有助于工程团队了解良率情况 。 Chiplet 信号路径缺陷可能会影响 PHY(即 I/O 电路)、从 Chiplet 到中介层再到封装衬底的冶金连接 , 以及相应的互连 。 由于需要驱动的传输线较短 , I/O 电路的设计布局在设计规则方面更为宽松 , 这反过来降低了 I/O 电路的故障率 。 同样 , 重分布层(RDL)和中介层互连不会突破工艺极限 。

lane 修复主要是为了解决与硅通孔(TSV)、微凸点和混合焊盘相关的组装工艺缺陷 。 历史上 , 只有一两个连接会受到缺陷的影响 。 然而 , 根据组装技术的不同 , 主要的缺陷机制可能会发生变化 , 有缺陷的连接数量也会增加 。

“如果使用间距为 25 微米的 EMIB(英特尔的嵌入式多芯片中介层桥接技术) , 主要的缺陷机制是开路 , 因为会产生更多的过孔 , ” 安晟培(Ampere)研究员、负责 Chiplet 互连测试和修复标准化的 IEEE P3405 工作组主席斯里吉特?查克拉瓦蒂(Sreejit Chakravarty)表示 , “因此 , 主要会遇到单 lane 故障 。 再看采用微凸点(间距小至 25 微米)的硅中介层 , 短路比开路更常见 。 会看到焊料凸点融合 , 导致相邻的两条 lane 短路 。 而在混合键合中 , 灰尘颗粒或某种杂质可能会进入两个表面之间 , 那么该灰尘颗粒周围的大量连接都无法正常形成 。 故障会成簇出现 , 影响两个以上的凸点 。 ”

过度翘曲和凸点 / 焊盘工艺偏差也可能影响多个连接点 , 尤其是在芯片和晶圆边缘 。 这些可能会导致多个开路或虚焊接触 , 最终在使用现场发生故障 。

lane 替换细节每个 Chiplet 的 I/O 以及 I/O 之间的互连构成一条 lane 。 lane 修复就是针对制造缺陷和现场故障替换有问题的 lane 。

不同的 Chiplet 接口标准在信号与备用 lane 的比例上存在差异 。

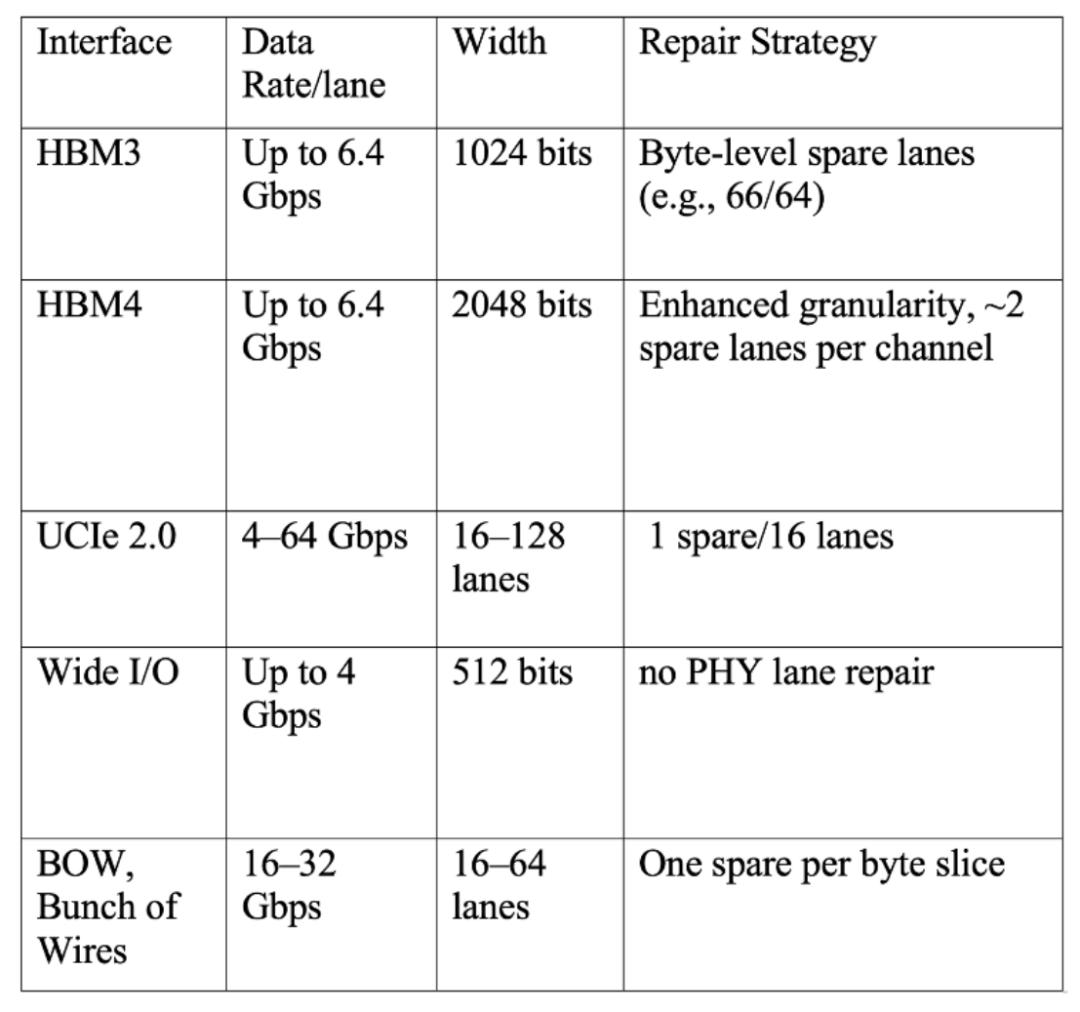

表 1:Chiplet 接口及其修复策略 。 来源:爱德万测试(Advantest)

“多芯片设计中另一个重要的考虑因素是 , lane 偏移必须在两个芯片中都实现 , ” 新思科技的戈里亚瓦拉表示 , “有故障的 lane 输出 I/O 随后会进入待机模式 。 对于数据中心 / 高性能计算和汽车等多芯片 IC 应用来说 , 这些都是重要的要求 , 因为从降低总拥有成本或安全性的角度来看 , 它们需要高可靠性 。 ”

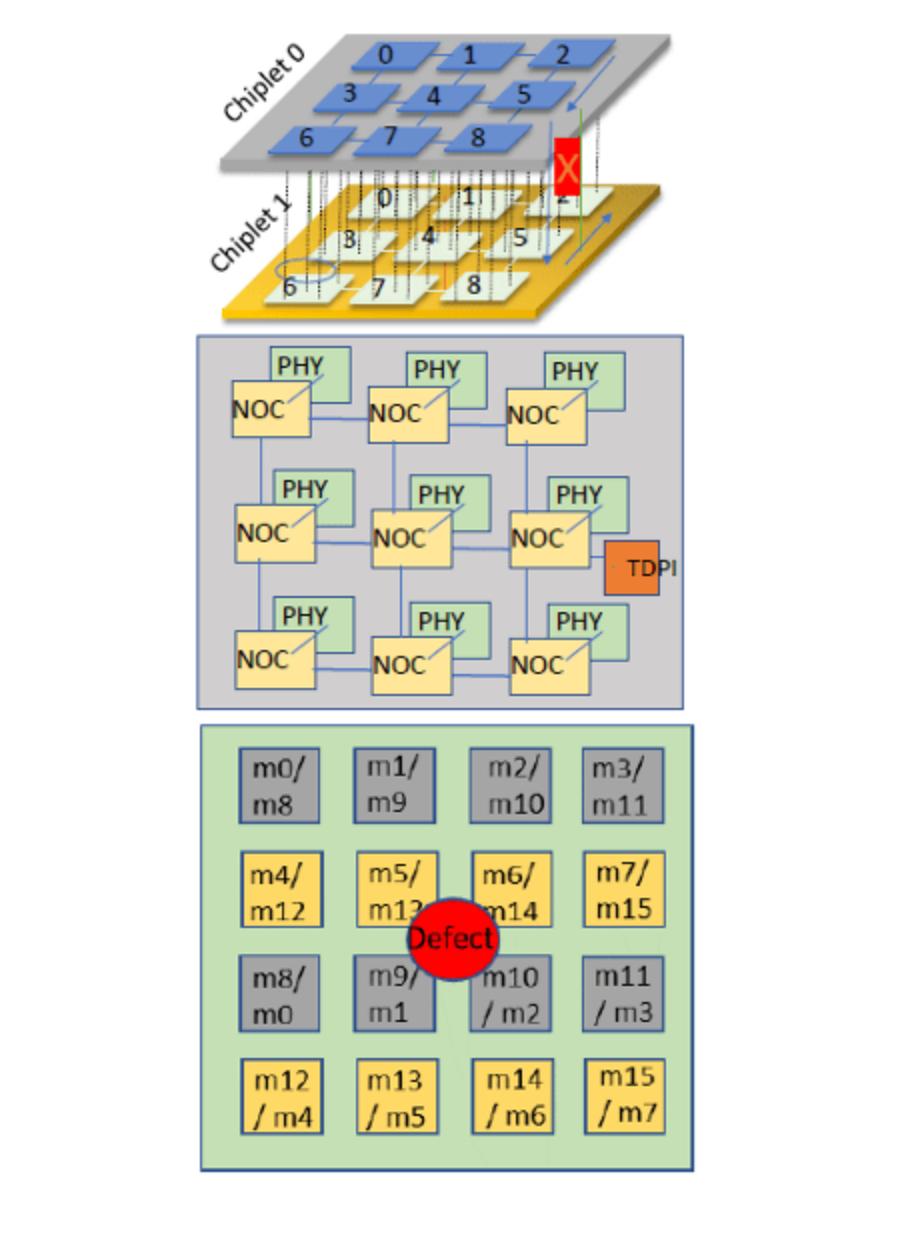

图 1:多芯片系统中的冗余 lane 。 来源:新思科技

对于 HBM 接口 , 研究团队仍在探索各种修复方案 。 在最近的一篇论文中 , 作者强调需要考虑成簇的 I/O 故障 。 虽然在出现成簇故障时可以采用优雅降级方案 , 但这会导致数据带宽显著降低 。

需要具备应对堆叠芯片场景中成簇故障的能力 。

拟议的 UCIe 3D 标准考虑到了故障成簇的情况 。 这对于采用混合键合的组装工艺来说非常重要 , 因为 5 至 10 微米的间距增加了两个以上混合焊盘受到颗粒影响的可能性 。

图 2:组装缺陷可能影响 3D 芯片堆叠中的多个连接 。 来源:UCIe 联盟

为有效应对这种情况 , 该标准将建议焊盘和 I/O 布局采用模块化设计 。 在去年的一次演讲中 , UCIe 联盟主席、英特尔高级研究员德本德拉?达斯?夏尔马(Debendra Das Sharma)讨论了这种方法 , 他指出一个缺陷可能会影响 5×5 的凸点 / 焊盘区域 。 因此 , UCIe 3.0 架构将设计成带有可用于修复的 I/O 模块 , 以及随后重新路由至冗余模块的功能 。

具体细节描述如下:

UCIe3D:每个模块有一个发射(TX)束(64 个 TX + 时钟)和一个接收(RX)束(64 个 RX + 时钟);

对于 9 微米的凸点间距 , 束布局大致为正方形 , 约 100 微米 ×100 微米;

【Chiplet 接口设计主动应对故障】对于密集排列的 2D UCIe 模块阵列 , 预留两个完整模块(四个束)以修复一个故障簇;

假设在至少一个方向上发射束和接收束交替排列 。

图 3:以束为单位的 UCIe 修复模块化 , 展示了未修复的行、一个束有缺陷时修复的行、一个缺陷影响四个模块时修复的两行 。 来源:UCIe 联盟

尽管如此 , 要充分实现异构集成 , 在不披露 Chiplet 专有内部设计的情况下实现 Chiplet 之间的连接 , 需要一种标准化的方法来测试 I/O 并修复 Chiplet 之间的连接 。

“如果购买的 Chiplet 带有 UCIe 或 HBM 接口 , 那么你会了解其标准协议 , ” 西门子 EDA 泰森特(Tessent)产品总监维迪亚?尼尔昆达(Vidya Neerkundar)表示 , “我该如何连接它?如何测试它?如何进行 lane 修复?现有的 Chiplet 互连标准都内置了用于这些操作的机制 。 但如今 , 当不知道另一个芯片的预期时 , 两个芯片之间的 I/O 没有标准流程 。 而 P3405 是一个拟议的标准 , 旨在解决这些情况下的 I/O 测试和修复问题 。 ”

P3405 对于实现互操作性至关重要 , 从而实现来自不同来源的 Chiplet 的集成 。 如果没有支持 Chiplet 之间 I/O 测试和修复的标准 , 这种集成就无法实现 。 P3405 定义了一种 I/O 测试和修复架构 , 用于验证 I/O 连接是否需要更换并执行修复操作 。 它还将应对成簇 I/O 故障的实际情况 。

“未来两年 , 高性能计算(HPC)将继续主导大多数 2.5D 和 3D 硅设计 , ” 爱德万测试美国公司测试技术销售总监鲍勃?巴特利特(Bob Bartlett)表示 , “对于 I/O 修复 , UCIe 和 HBM 足以推动异构集成 , 因为我们正开始采用更多的 3D 封装 。 但我认为这不再是测试成本的问题 , 而是良率成本的问题 。 当 3D 领域的所有设计工具都变得更好时 , 我们就能拥有成本更低的 3D 产品 。 这些产品将支持更多样化的应用 , 与高性能计算产品相比 , 它们更小、更简单且功耗更低 。 而对于 I/O lane 修复 , P3405 能够支持这些低成本应用 。 ”

制造测试实施测试可确定需要修复的 lane 。 每种冗余方案都会影响测试程序以及从晶圆到系统测试的测试插入 。 考虑到这一点 , 工程团队实施的实际测试流程可能会有所不同 。

“成本和质量始终是测试流程决策的驱动因素 , ” 泰克达因(Teradyne)首席技术专家兼战略业务发展总监肯?拉尼尔(Ken Lanier)解释道 , “在其他条件相同的情况下 , 平衡报废成本与测试成本 , 以实现最低的制造成本 , 这始终会决定在每个插入点(传统上是探针测试、封装测试、系统级测试和最终产品测试)要进行哪些测试 。 先进封装往往会使情况变得复杂 。 例如 , 芯片级封装、存储器堆叠和一般的多 Chiplet 封装 , 要么会使某些插入点的测试无法进行 , 要么会促使针对后期制造步骤中引入的故障进行测试 。 ”

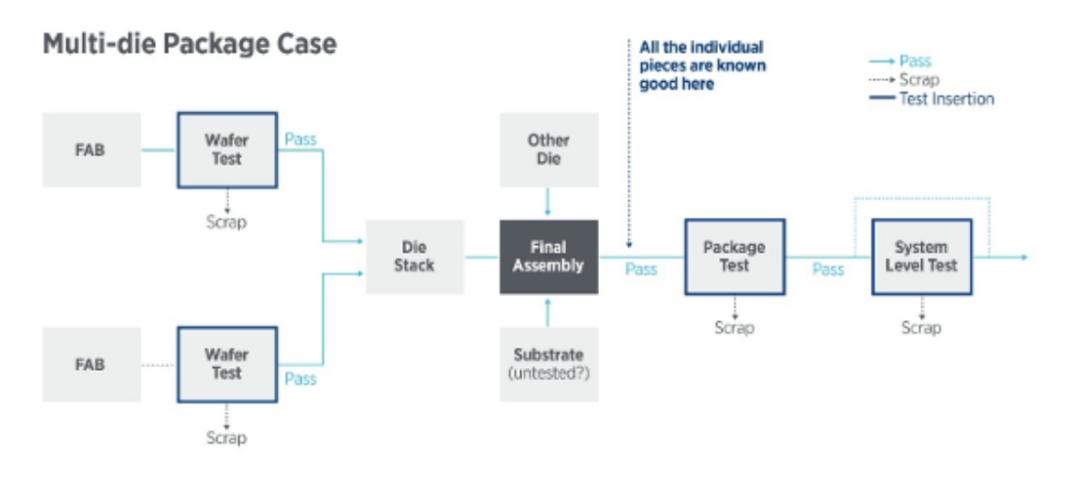

图 4:基于 Chiplet 的产品测试流程 。 来源:泰克达因

Chiplet 接口的晶圆测试和封装测试都需要可测试性设计(DFT)来提供访问和测试内容 。 在晶圆测试中 , 并非所有芯片的微凸点都会被探测 , 通常只探测测试焊盘 。 一旦完成组装 , 就无法通过自动测试设备(ATE)直接接触 Chiplet 接口 。 组装后的 I/O 测试需要包含针对桥接和开路缺陷的图形覆盖 。 由于凸点间距小且数据速率高 , 需要用适当的测试图形来激活耦合和串扰故障行为 。

图 5:高性能计算多芯片产品及有限的测试访问途径 。 来源:泰克达因(Teradyne)

“在晶圆级测试中 , 会执行内部和近端环回内置自测试(BiST) , 以测试本地的发射(TX)和接收(RX)部分 , ” 新思科技(Synopsys)的戈里亚瓦拉(Goriawalla)表示 , “特别是在芯片与芯片键合后阶段 , 需要执行远端环回内置自测试和芯片到芯片内置自测试 , 以覆盖两个 Chiplet 的发射和接收部分 。 这些测试中表明存在缺陷 lane 的结果需要写入物理层(PHY)的 lane 修复寄存器 , 并在不同的工艺、电压和温度(PVT)角落进行汇总 , 以便将最终的修复特征编程到本地的电子熔丝(e-fuse)/ 一次性可编程(OTP)元件中 。 对于后续的上电自检(POST) , 额外的步骤是我们需要先加载修复特征(在运行测试之前) , 以确保已知的缺陷 lane 无需重新测试 。 ”

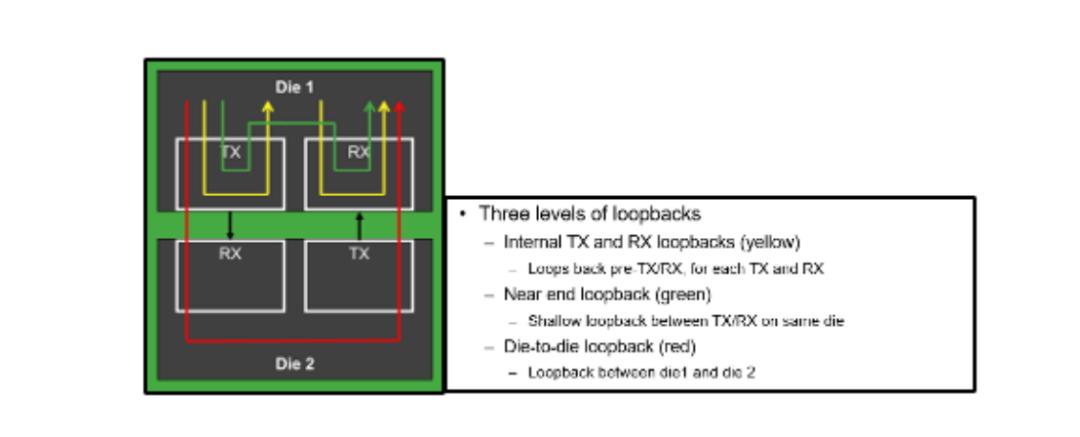

图 6:三种类型的 I/O 环回 。 来源:新思科技

至于 I/O lane 修复是否应在晶圆级测试时进行 , 这要视情况而定 。 如果主要的 I/O 互连故障与组装相关 —— 例如近端环回或直流测试中出现的 I/O 故障 , 芯片可能会被标记为不良品 , 但并非总是如此 。

“这完全取决于你希望最终测试达到多少良率 , ” 查克拉瓦蒂(Chakravarty)说 , “如果整个修复流程的良率很低 , 那么你可以考虑在晶圆测试时修复芯片 。 这种选择需要以数据为依据 , 因为你还需要组装芯片并测试封装后的产品 。 ”

如果客户要求在晶圆级测试时进行 I/O 修复 , 那么这会增加芯片的属性 , 以便将具有相似特征的芯片进行匹配 。 有关已修复 / 已替换 lane 的信息存储在电子熔丝 / 非易失性存储器(e-fuse/NVM)中 , 这使得匹配成为可能 。

“lane 修复信息存储在设备中 , 只要设备被重新配置为使用一定数量的冗余 lane(如果有的话)用于芯片到芯片接口 , ” 泰克达因的拉尼尔(Lanier)解释道 , “有趣的是 , 现在封装过程需要确保与已修复芯片相连的任何芯片都有一组匹配的可用 lane 。 这是基于 Chiplet 的设备在芯片匹配这一整体问题中的一个方面 。 ”

在替换之前 , 是否将冗余 lane 的测试作为测试过程的一部分 , 取决于客户需求 。 用于汽车、航空航天和其他安全关键应用的多芯片产品将需要对所有备用 lane 进行预测试 。

“假设我们有 30 条 lane 和 2 条备用 lane , ” 查克拉瓦蒂说 , “最初 , I/O 内置自测试将测试 30 条 lane 。 测试结束时 , 发现第 17 条 lane 有问题 。 内置自测试会将该信息提供给多路复用逻辑 , 用其中一条冗余链路替换第 17 条 lane 。 接下来 , 会重新运行 I/O 内置自测试序列 , 以确保连接良好 。 但对于大量的冗余 lane , 客户可能要求测试冗余 lane 是否正常工作 , 这可能需要在所有测试插入点进行 , 还需要在老化测试期间对冗余电路进行测试 。 ”

I/O 替换也可以在现场进行 , 以应对基于可靠性或老化的故障 。 当设备在测试流程结束时用尽所有备用 lane 时 , 这给设备制造商带来了一个难题 。 设备仍然可以运行 , 但没有备用 lane 了 。 一种可能的做法是根据剩余备用 lane 的数量对设备进行分档 。

“这是一个很好的问题 , 因为根据修复 lane 的数量对部件进行分档可能是有价值的 , ” 安靠科技(Amkor Technology)的制造测试技术专家维尼特?潘乔利(Vineet Pancholi)说 , “在技术不断成熟的过程中 , 这可能很重要 。 我们尚未观察到客户针对高性能计算和汽车领域的产品 , 根据制造后可用的修复 lane 数量对部件进行分档 。 一旦有足够的数据证明现场修复需求的好处 , 这种情况可能会改变 。 ”

泰克达因的拉尼尔对此表示赞同:“这取决于具体情况 。 如果是外部接口 , 或许你仍然可以将最终设备作为较低性能的版本出售 。 对于内部(芯片到芯片)总线 , 情况似乎也是如此 , 但这听起来确实很难管理 。 ”

结论就像存储器设备设计人员接受了位单元故障的现实一样 , 多芯片设备设计人员也在接受 lane 故障的现实 。 随着 Chiplet 互连数量达到数十万 , I/O 测试以及随后通过替换备用 lane 进行修复的做法将变得更加普遍 。

“这一切都归结为缺陷密度 , ” 爱德万测试(Advantest)的巴特利特(Bartlett)说 , “组装触点、微凸点、焊盘 —— 所有东西都在变得更小 。 混合键合的间距已达到 10 微米 , 并正朝着 5 微米迈进 。 你的 I/O 接口需要坚固耐用 。 你需要足够的可修复性 , 以确保设备能正常工作 10 年 。 而且 , 随着不断缩小 , 你将需要更多的修复能力 。 ”

或者简单地说 , 为了提高组装后的良率 , 冗余 lane 的需求已成为必要 。

*声明:本文系原作者创作 。 文章内容系其个人观点 , 我方转载仅为分享与讨论 , 不代表我方赞成或认同 , 如有异议 , 请联系后台 。

想要获取半导体产业的前沿洞见、技术速递、趋势解析 , 关注我们!

推荐阅读

- 彻底解开封印!红米新机迎来USB3接口,但这些升级更实在

- 苹果新机曝光,设计大改!

- iPhone 17 Pro 新设计曝光,信号变好了?

- 苹果 HomePod mini 2 即将发布,新设计首次曝光

- 荣耀Magic8系列突然入网:直屏设计+90W有线快充,多款机型蓄势待发

- 奥特曼公然叫板马斯克,重金杀入脑机接口,硅谷两大巨头彻底决裂

- 华为Mate80惊艳曝光:设计新高度,看完后直接点赞

- 荣耀 Magic V2 官宣:晨曦紫设计惊艳亮相,竖向折叠新风尚来袭!

- 阿尔特曼,要做脑机接口了

- OpenAI和奥特曼将投资一家脑机接口公司,直接与Neuralink竞争