文章图片

由芯师爷主办的“2025硬核芯”评选活动火热进行中 , 现以“云展览”的方式为您全方位展示中国芯产品及企业 。

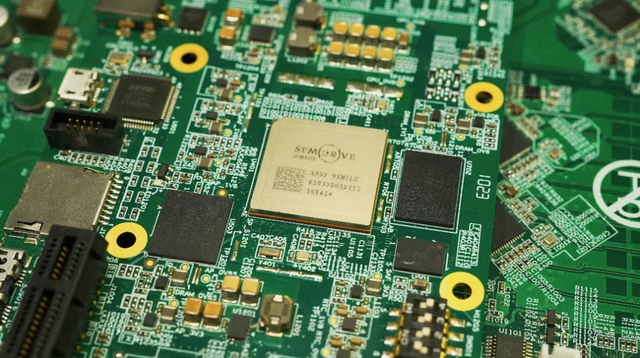

参评企业:芯驰科技

企业介绍

芯驰科技成立于2018年 , 在北京、上海、南京、深圳、大连设有研发中心 , 同时在长春和武汉设有办事处 。 芯驰团队的核心成员有近20年车规芯片量产经验 , 是国内为数不多的具备车规芯片产品定义、技术研发及大规模量产落地的国际化整建制团队 。 芯驰的核心IP自主设计 , 在全球范围拥有超330项自主知识产权 , 覆盖车规处理器关键核心技术 。

芯驰全系列芯片产品均已量产 , 出货量超800万片 , 拥有超200个定点项目 , 服务超过260家客户 , 覆盖国内90%以上主机厂及部分国际主流车企 , 包括上汽、奇瑞、长安、东风、一汽、日产、本田、大众、理想等 。

在车规认证方面 , 芯驰是国内首个完成车规芯片领域五大安全认证的企业 , 先后获得了莱茵TüV ISO 26262 ASIL D功能安全流程认证、AEC-Q100 Grade 1/Grade 2可靠性认证 , ISO 26262 ASIL B/ASIL D功能安全产品认证 , ISO/SAE 21434汽车网络安全管理体系认证 , 以及由工商总局、国家密码管理局颁发的国密信息安全双认证 。

在智能座舱领域 , 芯驰X9系列智能座舱芯片以家族化的产品布局 , 全面覆盖3D仪表、IVI、座舱域控、舱泊一体等从入门级到旗舰级的座舱应用 , 并且在积极引领AI座舱的产品发展 。 在智能车控领域 , 芯驰E3系列车规MCU已广泛应用于区域控制、车身控制、电驱、BMS电池管理、智能底盘、ADAS智能驾驶等核心领域 。

产品一:芯驰科技E3650

作为自主高端车规MCU芯片新标杆 , E3650采用ARM R52+锁步多核 , 600MHz主频领跑同级 , 确保实时性与安全 。 集成16MB存储与高于4MB的大容量SRAM , 满足域控高算力、快响应需求 。

针对跨域融合的复杂性 , E3650提供专为域控场景设计的虚拟化解决方案 , 高效实现业务隔离与代码集成;此外E3650还集成多外围器件及丰富GPIO , 具有超过350个可用外设IO , 大幅节省外围IO扩展芯片、有效降本;内置硬件通信加速引擎 , 降低延迟丢包和CPU负载 。 安全上 , 集成高性能信息安全模块模块 , 支持国密算法 , 满足ISO 21434等全球高标准 , 构筑顶级防护 。

值得一提的是19x19mm紧凑尺寸 , 可有效助力控制器极致小型化 。 E3650可全面覆盖整车区域控制器、VMC底盘域控、智舱/智驾域控、动力域控四大核心应用场景 。

产品二:芯驰科技X9SP

芯驰科技以单座舱芯片X9SP实现了智能座舱与泊车功能的深度融合 , 实现了多屏联动流畅无卡顿、语音指令秒级响应、环视影像实时校准、DMS面部特征毫秒级追踪;同时还实现泊车轨迹厘米级规划 , 在保障行车安全的基础上 , 让自动泊车系统可智能规避盲区障碍 , 完成复杂场景下的精准停泊 。 目前 , 基于X9SP的舱泊一体解决方案已获得多家客户认可和合作 。

算力配置:

(1)CPU资源:100K DMIPS

双GPU架构:仪表与中控域硬件隔离 , 无虚拟化开销 , 支持跨域冗余算力调用

(2)NPU:8TOPS算力 , 同步支持DMS/OMS与APA算法并行部署

(3)ISP:1Gpixel/s处理能力 , 支持Camera RawData调优

(3)VPU:多格式编解码能力 , 最高支持4K@60fps

安全架构:

(1)独立安全岛:可替代外置MCU , 按照ISO 26262 ASIL D功能安全设计 , 部署泊车控制、超声感知处理和泊车数据交换处理逻辑 。

(2)接口支持:双路CANFD , xSPI可挂载OSPI/QSPI 。

(3)软件架构:AutoSAR+FuSalib框架 , 提供功能安全监测能力 。

软硬件兼容:

【2025硬核芯云展览:芯驰科技,布局全场景智能车芯,赋车以魂!】与上一代X9HP保持Pin-to-Pin兼容架构 , 并采用同一套软件基线 , 支持车型快速升级与量产 , 大幅缩短开发周期 。

推荐阅读

- 从奥斯卡领奖台到BIRTV:DJI大疆专业影像生态亮相BIRTV 2025

- 2025 AI主战场,连锁门店“变形记”

- 2025硬核芯云展览:屹立芯创压膜系统撬动百亿封装除泡市场

- 苹果买对不买贵!2025年推荐这4款机型,3千到8千覆盖所有需求

- 2025硬核芯云展览:江波龙自研eMMC Ultra,重构嵌入式存储性价比

- 2025硬核芯云展览:格创东智,Al驱动的工业智能解决方案提供商

- 2025年全球折叠手机市占预估:华为市占有望达34.3%

- 2025年平价投影仪推荐:有了这两款,在家就能拥有影院级体验

- 2025全球折叠屏手机出货量预估,国产发力,三星份额或进一步减少

- 数字赋能智慧政务,华为擎云亮相2025政法智能化建设技术装备展