文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

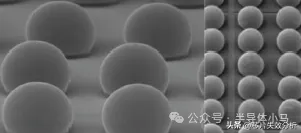

一、Bump介绍

在先进封装中 , “Bump” 通常指凸块 , 是一种关键的连接技术 。 它是在芯片表面制作的小凸起 , 一般只有几十到几百微米大小 , 主要作用是提供芯片与其他电子元件之间的电气连接 , 从倒装焊FlipChip出现就开始普遍应用了 , Bump的形状也有多种 , 最常见的为球状和柱状 , 也有块状等其他形状 。 Bump起着界面之间的电气互联和应力缓冲的作用 , 从Bondwire工艺发展FlipChip工艺的过程中 , Bump起到了至关重要的作用 。

随着工艺技术发展 , Bump尺寸越来越?。 築ump的发展趋势是尺寸不断缩小 , 从球栅阵列焊球(BGA ball) , 其直径范围通常在0.25-0.76mm , 到倒装凸点(FC Bump) , 也被称为可控塌陷芯片焊点(C4 solder joint) , 其直径范围通常在100-150μm 。 行业内正朝着 20μm 甚至小于 10μm 的方向推进 , 凸点间距越小 , 凸点密度越高 , 封装集成度越高 , 技术难度也越大 。 对于 20μm 以上的间距 , 可采用基于热压键合(TCB)的微凸块连接技术 , 未来混合键合(HB)铜对铜连接技术有望实现 10μm 以下的凸块间距和更高的凸点密度 , 并带动带宽和功耗双提升 。

工艺流程:通常包括清洗、溅镀、曝光、显影、电镀、去胶、蚀刻和良品测试等环节 。 具体而言 , 先在晶圆表面沉积钛或钛钨作为阻挡层 , 再沉积铜等作为种子层;然后旋涂光刻胶 , 通过光刻曝光和显影得到所需图形;接着进行电镀形成凸点下金属化层(UBM) , 去除光刻胶并蚀刻掉多余的种子层和阻挡层;之后进行植球工序 , 将助焊剂和锡球印刷到 UBM 上;最后经过回流炉使锡球熔化与 UBM 形成良好结合 。

凸块制造技术是诸多先进封装技术实现和发展演化的基?。 壕嗄甑姆⒄?, 凸块制作的材质主要有金、铜、铜镍金、锡等 , 不同金属材质适用于不同芯片的封装 , 且不同凸块的特点、涉及的核心技术、上下游应用等方面差异较大 。

一、金凸块

主要特点:

优点:高导电性、抗腐蚀性强、键合工艺成熟、无需底部填充(Underfill) 。

缺点:成本高(黄金价格昂贵)、硬度低易变形、高温下可能与焊料形成脆性金属间化合物(IMC) 。

关键参数:典型尺寸为 50-150μm , 间距 100-250μm 。

应用领域:1)高频、高可靠性器件:RF模块、光通信器件、毫米波雷达;2)医疗、航空航天:植入式医疗设备、卫星电子元件;3)Flip Chip 封装早期应用:如早期手机芯片、FPGA 。

工艺流程:

二、铜镍金凸块

主要特点:

优点:结合铜的低成本和金的抗腐蚀性 , Ni 层作为扩散阻挡层抑制 Cu-Sn IMC 生长 。

缺点:工艺复杂度高(三层金属沉积) , 需严格控制 Ni 层厚度(过薄易穿透 , 过厚易脆) 。

关键参数:Cu柱高度50-100μm , Ni层厚度3-5μm , Au层厚0.3-1μm 。

应用领域:1)汽车电子:ECU(电子控制单元)、功率模块;2)工业设备:高可靠性传感器、控制器;3)消费电子:中高端手机摄像头模组、指纹识别芯片 。

工艺流程:

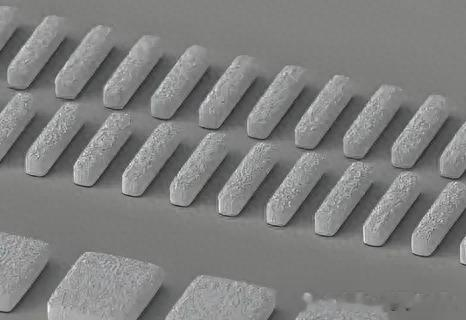

三、铜柱凸块

主要特点:

优点:低电阻(铜导电性优于锡)、高热导率、更好的机械稳定性(抗跌落测试)、适合细间距(≤50μm) 。

缺点:易氧化(需表面处理)、Cu-Sn IMC 生长可能导致可靠性问题 。

关键参数:Cu柱直径 10-50μm , 高度 30-60μm , 表面通常有 Ni/Au 或 Sn/Ag 涂层 。

应用领域:1)高性能计算:CPU、GPU、HBM(高带宽内存);2)5G 通信:RF 前端模块、高速 SerDes 芯片;3)AI 芯片:需要高密度 I/O 的 ASIC、FPGA 。

工艺流程:

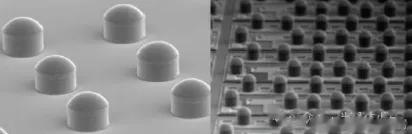

四、锡凸块

主要特点:

【先进封装四要素介绍】优点:工艺简单、成本低、自对准能力强(回流时液态表面张力) 。

缺点:电性能较差(电阻高于铜)、热循环可靠性有限(锡易疲劳) 。

关键参数:典型成分为 SnAgCu(SAC)合金 , 尺寸 30-200μm , 间距 50-400μm 。

应用领域:1)消费电子:智能手机、平板电脑、可穿戴设备;2)存储芯片:DDR、NAND Flash 封装;3)低成本/中低端器件:如 WiFi 模块、蓝牙芯片 。

工艺流程:

五、技术对比与选择标准

凸块类型

成本

电性能

热性能

可靠性

工艺复杂度

最小间距

典型应用

金凸块

高

优

良

优

低

100μm+

RF 器件

医疗设备

铜镍金凸块

中

良

良

优

中高

80μm+

汽车电子

工业控制

铜柱凸块

中

优

优

良

高

≤50μm

HPC

5G

AI 芯片

锡凸块

低

良

中

中

低

50μm+

消费电子

存储芯片

六、Bump在Flip Chip(倒片封装)中的应用

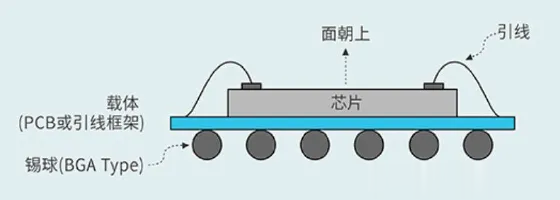

倒片封装技术因其将芯片上的凸点翻转并安装于基板等封装体上而得名 , 是一种实现芯片与板(如基板)电气连接的互连技术 , 键合至基板或形成焊接凸点过程中不存在任何工艺方面限制;倒片封装凭借其优越的电气性能(不存在电气连接I/O引脚数量和位置限制 , 电信号传输路径短于引线键合) , 已经很大程度上取代了引线键合 。 倒片封装体中凸点(Bump)是基于晶圆级工艺而完成的 , 而后续工序则与传统封装工艺相同 。

引线键合示意图

倒装芯片绑定示意图

倒装芯片凸点制作工艺流程

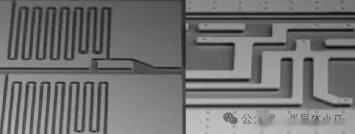

二、RDL介绍

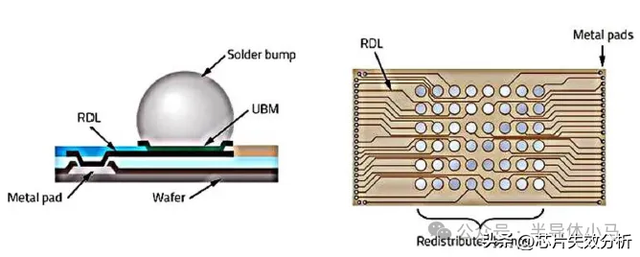

RDL(Redistribution Layer)即重分布层 , 是先进封装中实现芯片水平方向电气延伸和互连的关键技术 , 在 3D/2.5D 封装集成以及 FOWLP(扇出型晶圆级封装)中应用广泛 。

一、工作原理

通过在芯片表面沉积金属层和相应的介电层 , 形成金属导线 , 将 IO 端口重新设计到更宽敞的区域 , 构建出表面阵列布局 。 简单来说 , 就是把芯片原本位于边缘或四周的 I/O 触点 , 通过半导体工艺延伸到芯片表面其他位置 , 扩展布局到占位更宽松的区域 , 实现 I/O 触点的重新布线 。

二、优势

降低设备成本:打破了传统封装中昂贵且耗时的引线键合和倒装芯片键合工艺的束缚 , 通过减少设备所需的元件数量 , 有效降低设备成本 。

减少占地面积:可将多个芯片集成到单个封装中 , 极大地减少器件的整体占地面积 , 满足智能手机、可穿戴设备等对空间要求极高的产品需求 。

改善电气性能:RDL 中介层信号通孔尺寸极小 , 可大幅改善 SerDes 信号完整性 , 其金属厚度优势也能提升内存 SI , 同时低损耗介电材料可降低介电损耗 , 优化整个封装的电气性能 。

提高设计灵活性:RDL介质层利用精细的线路宽度和间距 , 减少路由干扰 , 支持更多引脚数量 , 使 I/O 触点间距更灵活 , 凸点面积更大 , 为芯片设计提供更大自由度 。

三、工艺流程

在重新分配层工艺中 , 首先通过溅射工艺创建一层金属薄膜 , 之后在金属薄膜上涂覆厚层光刻胶 。 随后利用光刻工艺绘制电路图案 , 在电路图案的曝光区域电镀金层 , 以形成金属引线 。 由于重新分配工艺本身就是重建焊盘的工艺 , 因此确保引线键合强度是十分重要的 。 这也正是被广泛用于引线键合的材料—金 , 被用于电镀的原因 。

四、应用领域

RDL 技术已广泛应用于MEMS器件、传感器、功率器件、存储器、微处理器和图形处理器等众多领域的封装 , 为实现更小、更快、更高效的芯片设计提供技术支撑 。

在WLP中:在FIWLP/FOWLP中 , RDL是最为关键的技术 , 通过RDL将IOPad进行扇入Fan-In或扇出Fan-Out , 形成不同类型的晶圆级封装 。

在2.5D中:除了硅基板上的TSV , RDL同样不可或缺 , 通过RDL将网络互联并分布到不同的位置 , 从而将硅基板上方芯片的Bump和基板下方的Bump连接 。

在3D中:对于上下堆叠是同一种芯片 , 通常TSV就可以直接完成电气互联功能了 , 而堆叠上下如果是不同类型芯片 , 则需要通过RDL重新布线层将上下层芯片的IO进行对准 , 从而完成电气互联 。

五、技术发展

目前 4 层 RDL 技术已经成熟 , 良率可达 99% , 能满足约 85% 的封装需求 。 未来 , RDL 工艺将朝着提高粘附力 , 减少热循环过程中的机械应力和热应力的方向发展 , 同时对布线检测等设备也提出了更高要求 。

三、Wafer

在先进封装四要素中 , Wafer(晶圆)是集成电路的基础载体 , 也是RDL 和TSV的介质和载体 。

一、材料与结构

晶圆通常是薄片状的硅片 , 现代晶圆几乎是纯硅材料 , 杂质含量极低 , 晶体结构需非常完美 , 以避免制造过程中产生缺陷 。 此外 , 还有化合物半导体材料晶圆 , 如氮化镓(GaN)和碳化硅(SiC)晶圆 , 适用于 5G 通信、射频器件和电动汽车等高端应用场景 。

二、尺寸规格

其尺寸(直径)随着工艺进步不断扩大 , 早期晶圆直径只有几英寸 , 现代已达到300mm(12 英寸) , 甚至正在开发450mm(18 英寸)的晶圆 。 更大的晶圆尺寸意味着一片晶圆上可加工的芯片数量增加 , 能提高生产效率并降低成本 。

三、作用与功能

晶圆是制造集成电路(IC)的平台 , 所有的芯片电路都在晶圆上进行加工形成 , 每一个芯片(Die)都是从晶圆上切割下来的 。 同时 , 可以在Wafer上制作硅基板实现2.5D集成 , 也是 WLP(晶圆级封装)的承载晶圆 。

四、工艺要求

为满足芯片尺寸不断缩小和集成度不断提高的需求 , 对晶圆纯度、平整度和结构缺陷控制要求极高 。 晶圆制造需在高度控制的环境下进行 , 包括生长单晶硅棒、切割、抛光和清洗等一系列复杂工艺 。

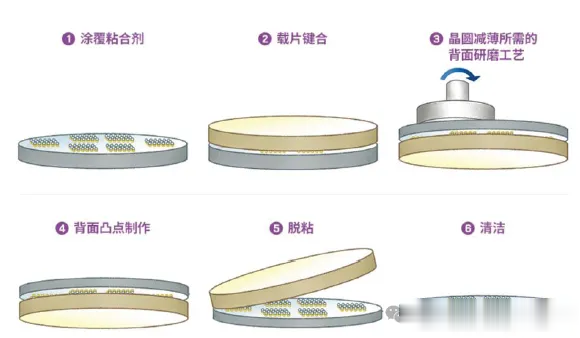

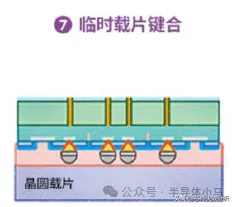

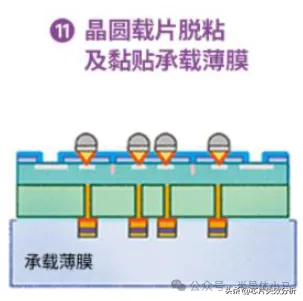

晶圆承载系统工艺:是指针对晶圆背面减薄进行进一步加工的系统 , 该工艺一般在背面研磨前使用 。 晶圆承载系统工序涉及两个步骤:首先是载片键合 , 需将被用于硅通孔封装的晶圆贴附于载片上;其次是载片脱粘 , 即在如晶圆背面凸点制作等流程完工后 , 将载片分离 。

晶圆边缘切筋工艺:对于采用硅通孔工艺封装的晶圆 , 在其进行载片键合前 , 应先对晶圆正面边缘进行切筋并去除修剪部分 。

五、发展趋势

随着先进封装技术向更小的节点(如3nm、2nm)发展 , 晶圆制造工艺也在不断进步 , 将更依赖于不同类型晶圆(如硅基和化合物半导体基晶圆)的结合 , 以实现高效能的芯片封装和集成 。

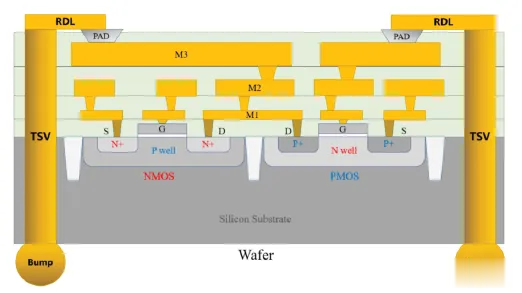

四、TVS介绍

TSV(Through - Silicon Via , 硅通孔)是先进封装技术中的一种关键垂直互连技术 。 它通过在芯片内部打通通道 , 实现电气信号的垂直传输 , 可显著提高芯片之间的数据传输效率 , 减少信号延迟 , 降低功耗 , 并提升封装的集成密度 。

一、工作原理

基于硅片中的深孔刻蚀技术 , 先在硅片中打孔 , 再填充铜等导电材料形成电气连接 。 这些通孔贯穿整个芯片厚度 , 可将不同芯片层或同一芯片内的不同电路相互连接 , 作为芯片与芯片、芯片与封装基板、以及芯片内部不同电路层之间的高效电气通道 。

二、分类

2.5D封装中的TSV:通常用于中介层(Interposer) 。 中介层是带有 TSV 的载体 , 可承载多个芯片 , 如处理器和内存等 , 芯片通过 TSV 在中介层上互连 , 而非直接堆叠 , 主要应用于高性能计算和数据中心芯片等需要高度互连和高带宽的系统 。

3D 封装中的 TSV:实现了芯片的垂直堆叠 , 每个芯片层通过 TSV 直接相互连接 , 形成一个整体 , 能让不同功能模块 , 如处理器和内存高度集成在同一个封装中 , 提高芯片集成密度和性能 , 同时减小封装尺寸 。

Via-last TSV:TSV制作可以集成到生产工艺的不同阶段 , 通常放在晶圆制造阶段为Via-first , 封装阶段为Via-last(该方案可以不改变现有集成电路流程和设计 , 目前业界已开始在高端的Flash和DRAM领域采用Via-last技术 , 即在芯片周末进行硅通孔的TSV制作 , 然后进行芯片或晶圆层叠 。

Via-middle(中通孔)封装工艺:首先在晶圆制造过程中形成通孔 , 随后在封装过程中 , 于晶圆正面形成焊接凸点 。 之后将晶圆贴附在晶圆载片上并进行背面研磨 , 在晶圆背面形成凸点后 , 将晶圆切割成独立芯片单元 , 并进行堆叠 。

三、工艺流程

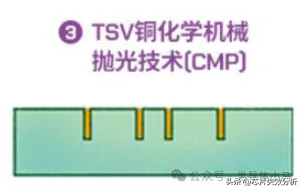

中通孔基本工序:首先在晶圆上制作晶体管 , 随后使用硬掩模在硅通孔形成区域绘制电路图案 , 之后利用干刻蚀工艺去除未覆盖硬掩膜的区域 , 形成深槽;再利用CVD工艺制备绝缘膜(用于隔绝填入槽中的铜等金属物质 , 防止硅片被金属物质污染);此外绝缘层上还将制备一层金属薄层(将被用于电镀铜层)作为屏障;电镀完成后 , 采用CMP技术使晶圆表面保持平滑 , 同时清除其表面铜基材 , 确保铜基材只留在沟槽中 。

来源:半导体封装工程师之家

推荐阅读

- 半导体封装生产线工艺流程研究

- 揭秘 IGBT 模块封装与流程

- 芯片封装失效典型现象

- 北方华创发布12英寸先进低压化学气相硅沉积立式炉设备

- 台积电盯上的SoW封装,到底是什么?

- 被低估的芯片封装:院士称我们落后国际,可能2-6年

- 比苹果先进2年!华为最激进的手机曝光:外观性能太猛了

- 新EDA工具推出,用于小芯片集成、封装验证

- 华为申请“四芯片”封装专利 布局下一代AI芯片昇腾910D

- 苹果在尝试利用生成式人工智能设计芯片 高管称设计芯片需要先进工具