文章图片

文章图片

Q1

芯片金属层之间的通孔VIA , 英文全称是什么?

A1

via就是全称 , 本身就是一个英语单词 。

Q2

解完UV后 , 膜的粘度有几十mN/25mm的 , 有几百mN/25mm的 , 这种在选择的时候有什么rule吗?粘度到多少工厂才会难摘?。 ?

A2

参考短边die size 。

Q3

【?芯片分析问答2025.7.9】

low k制程(比如40nm)的芯片 , 大家有遇到过弹坑问题引起的早夭失效的案例吗?

Al制程有遇到过弹坑问题导致的早夭失效 , 但是low k制程的我自己目前没有遇到过弹坑问题导致早夭失效的案例 。

A3

Low k失效风险更高 , low k机械强度弱 , CTE也高 , 对机械和温变应力都更敏感 。

Q4

芯片做完TC(-65~150度)500cycle后 , 有发现Bump和RDL侧面轻微delamination , 这种要按照JEDEC的哪个标准来判断是可接受还是不可接受的?

A4

J-STD-020E标准中有对分层的判定标准 , die区域是不能有分层的 。

Q5

是否有遇到过QFN车规芯片有经过三温测试 , 出现Die裂的情况?

A5

三温的顺序 , 是否pass , 在每种温度下warpage的数据 , pogo pin有没有卡住 , 都要考虑 。

Q6

硅凝胶怎么去除?

A6

用专门的溶胶剂 , 溶胶剂也不贵 。

Q7

晶圆从厂里出货后 , 包装原封不动的话 , 可以自己保存吗?自己暂存需要什么条件?

A7

氮气柜25左右温度保存 。

Q8

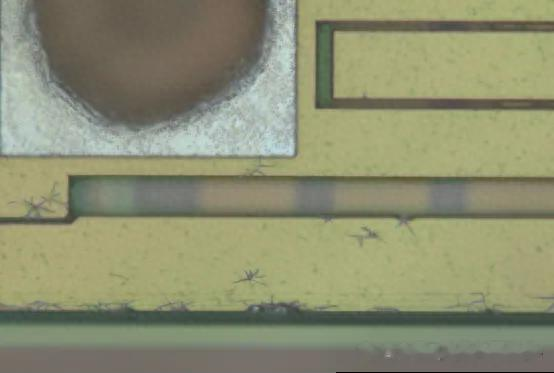

如下图Decap后看到的裂纹可能是什么原因导致的?

A8

这种不是应力造成的 , 去查sawing工艺 , 基本上是sawing的diamaflow出了问题 , CO2 bubble打少了 , 在sawing的过程中电荷没有及时导出 , 局部放电导致的 , 可以随便切一个位置看一下 , top metal会有静电击穿的现象 , 就像长出了一根天线 , 而且passivation已经碎了 , 可靠性肯定会有问题 , 不建议出货 。

Q9

现在PMIC这个赛道 , CP/FT的生产测试都用的哪个测试平台?

A9

要看这个PMIC的复杂程度 , 一般的8200能搞定 , 也可以看看ETS和8300 。

Q10

芯片的射频输入口 , 在FT测试都很正常 , 贴片后被静电损伤的很多 , IV曲线正常 , 但是LNA的增益和对地阻抗下降很多 , 像是通过CDM模式放电损坏的 , 这个有什么办法避免吗

A10

这个不一定是静电 , 如果是CDM的话 , 那就是加工过程中机台接地不好 , 也要看一下焊锡材料 , 焊锡厚度这些是不是符合之前的生产标准 , 有没有生产波动 , 一般来说批次性的问题 , 和生产品质相关性比较大 。

11

CSP封装的芯片 , 想排查一下是否因应力损坏X-ray能看出来吗?

A11

不能 , X-ray会直接穿透 , 建议利用3D-OM六面检查 。

Q12

IR是什么设备?

A12

红外线 , 可以看隐裂 , chip内部crack & chipping 。

Q13

AEC-Q100做HAST时 , 要求每个被测单体样品都处于正常工作状态吗?我们有一款产品需要SPI通信发送唤醒指令才会正常输出 , 否则就处于待机状态 , 在待机状态下可以做HAST吗?

A13

唤醒指令后器件就不是属于最低功耗状态了 , 不需要唤醒 。

Q14

为满足以下需求 , 该如何确认实验时长?

满足T_USE=85摄氏度 , 寿命10年的 HTOL 考核条件:

1. T_SRTESS= 150度 ,

V_SRTESS=1.1*VCC工作电压 ,

考核时长>=?

2. T_SRTESS= 125度 ,

V_SRTESS=1.1*VCC工作电压 ,

考核时长>=?

A14

Tuse最好有mission profile , 按照85度预估 , 150度stress时间就要2000hrs左右了 。

Q15

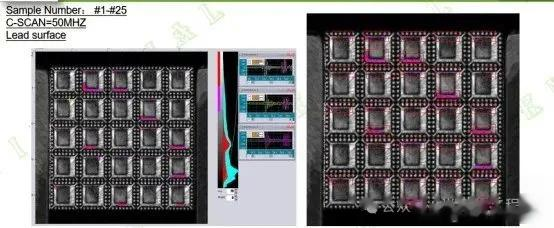

我们一颗产品TC后pad全是分层 , 如下图 , 正常吗?

A15

这张 C SCAN 扫描看起来是 die surface 正下方及周围有脱层 , 可以发一下 T SCAN 进行佐证 , 所以您这个应该是背晶位置脱层了 。 由于您这个是做 TC 之后的样品 , 明确指向温度相关 , 故优先确认封装的材料各膨胀系数关系 。 上图 die surface /lead frame 没发现脱层 , 所以排除由外而内的应力或脱层 。

Q16

BHAST 3批是按照三个wafer批次来做还是三个封装批次?

A16

验封装的 , wafer批次/封装批次不关键 , 你隔一周release一批最好 。

Q17

QFN做完BHAST(130℃/85%RH , 96hr)后失效 , EDX发现背面lead间EMC表面有大量Sn(>20%)和Cu(>4%)的成分(图上点状物) , 想问下这可能是电迁移吗?什么情况才会造成这样的现象?

A17

吸氧腐蚀的可能性比较大 , 镀层应该可以看到腐蚀掉了(薄了) , 有一种可能是做完Precon以后要做SAT如果是放在Tray盘里做SAT的 且拿出来以后水没有吹干 , 则会在镀层表面形成一层水膜 , 这时候就会发生吸氧反应 。

Q18

车规QFN产品pin pitch最小有要求0.5mm吗 , 有什么文件定义吗?

A18

行业不会有这个定义 , 要么也是你的客户公司有此内部规则 。

Q19

晶圆从厂里出货后 , 包装原封不动的话 , 可以自己保存吗?自己暂存需要什么条件?

A19

氮气柜25左右温度保存 。

Q20

Corner wafer的ESD , LU还需要单独评估吗?

A20

没这个要求 , 除非设计师希望收集这数据做比对 。

Q21

HBM实验会影响FT的SCAN测试吗?

A21

有可能会有影响的 , 毕竟HBM是一个破坏性实验 。

Q22

关于HTOL的寿命换算要根据power on时间和mission profile , 这两个有更具体的定义吗?

A22

这两项都是根据终端应用场景定义的 。

Q23

消费级芯片工作温度0-70℃ , 是哪个JEDEC文件定义的 , 为什么不能0°以下工作?

A23

芯片设计就是匹配0°以上使用场景的 。

Q24

FPGA产品一定要做SER吗?如果做SER , 放射源推荐什么?Alpha源还是X-ray类高能光束?

A24

内部有memory一般才需要SER , SER放射源看场景 , 一般推荐中子源和阿尔法源 。

Q25

PBO也是类似PI的passivation材料吗?

A25

应用领域差不多 , 类似于低温PI , 目前也就WPR系列封装有在用 。

Q26

BGA从板子上拆下来之后 , 锡球焊接不上 , 要怎么修复?确定焊盘没有损坏 , 可能需要清洗 , 如果需要清洗的话 , 一般怎么个清洗流程?

A26

用1%稀硫酸+超声波洗一下试试 , 大概十几秒到半分钟 。

来源:季丰电子

推荐阅读

- 小米厉害!首款3nm芯片玄戒O1,已杀入手机性能前4名

- 铠侠推出UFS 4.1闪存:最高1TB,BiCS8芯片打造

- 苹果将推出全新Vision Pro:搭载M4芯片、升级版神经网络引擎

- NVIDIA AI芯片成“新黄金”!市值全球首超4万亿美元只是开始

- 从CPU,到GPU,到Soc,中国已有自主研发的高性能芯片了

- 小米YU7,使用消费级芯片,藏着雷军大大的野心

- 10年了,三星旗舰自研手机芯片回归中国,加入高通联发科小米3nm芯大战

- IBM推出下一代Power11服务器

- 荣耀放弃高利润!16GB+512GB下跌1790元,骁龙8系芯片+50倍变焦

- 英伟达GB10超级芯片获多家PC品牌采用,即将大量出货