文章图片

文章图片

DRAM制程如何突破 10nm?这曾是困扰行业的共同课题 。

近日 , SK海力士带来了它的答案 。

本周 , 2025年IEEE VLSI 研讨会在日本东京举行 , 会议上SK海力士提出了未来30年的新 DRAM 技术路线图 。

SK 海力士表示 , 4F2 VG和3D DRAM技术将应用于10nm及以下级内存 。

至于10nm DRAM如何成为制程技术的难点?未来30年DRAM市场为什么依赖3D?4F2 VG技术又是什么?笔者在下文一一说明 。

011c DRAM , 龙头齐聚

一直以来 , 各大内存厂商将上一代DRAM芯片按照1X、1Y、1Z进行工艺区分 , 1Xnm工艺相当于16-19nm制程工艺、1Ynm相当于14-16nm制程工艺 , 1Znm工艺相当于12-14nm制程工艺 。 而新一代的1a、1b和1c则分别代表14-12nm、12-10nm以及10nm及以下制程工艺 。

为什么说10nm , 是DRAM技术进程中的绊脚石?

随着10nm制程的临近 , 使其在晶圆上定义电路图案已经接近基本物理定律的极限 。 由于工艺完整性、成本、单元泄漏、电容、刷新管理和传感裕度等方面的挑战 , DRAM存储单元的缩放正在放缓 。

法国分析机构Yole指出 , 即使通过光刻EUV 工艺 , 平面缩放也不足以在整个下一个十年提供所需的位密度改进 。

1c DRAM及接下来的发展很难 , 但这扇大门已被存储三大原厂叩响 。

去年8月 , SK海力士宣布完成第六代10nm级(1c)工艺DRAM 开发 。 当时SK海力士就曾强调:随着10nm级DRAM技术的世代相传 , 微细工艺的难度也随之加大 。 其中需要注意的一个点是 , 早在2021年SK海力士就已经开始将EUV应用于其10nm级第四代DRAM 。

今年2月 , 美光宣布已向生态系统合作伙伴及特定客户出货专为下一代 CPU 设计的 1γ(1-gamma)第六代(10 纳米级)DRAM 节点 DDR5 内存样品 。

三星的第六代10纳米级1c DRAM制程开发进度出现了延迟 , 预计完成时间从2024年年底推迟至2025年6月 。 这也意味着 , 本月或许就能看到三星新成果的推出 。

【DRAM,开启30年“新赌局”】此前韩媒报道 , 在下一代的HBM4内存开发上 , 三星和SK海力士正计划使用1c制程的DRAM 。

而随着1c纳米制程DRAM 商业化 , EUV光刻制造成本将快速攀升 。 现在来看 , 1c DRAM技术的发展似乎变得紧迫起来 。 接下来该怎么走?如何走?

3D DRAM便是那个最被看好的选手 。

3D DRAM可降低成本、最大限度地降低功耗并提高速度 。

SK 海力士表示 , 采用VG 或3D DRAM 制程设计 , 可将EUV 制程成本降一半 。

上图可见 , 再往后的10nm以下节点 , 将分别命名为0a、0b、0c、0d , 其中打头的0a工艺预计2027年底-2028年初量产(月产能超过2万块晶圆) , 0d则要到2032年 。

如果说2030年DRAM市场将高度依赖3D , 毫不夸张 。

那么 , 4F2 VG DRAM技术又是什么?

4F2 VG DRAM的设计灵感来源于NAND闪存 , 采用了混合键合技术 。 这是一种经过大量研究的单元阵列结构 , 其中晶体管以垂直方式堆叠 , 也就是3D DRAM 。 三星将这种3D DRAM 称为“垂直通道晶体管”(vertical channel transistor , 简称VCT) 。

4F2结构从下而上依序为源极(source)、闸极(gate)、汲极(drain)和电容器(capacitor) 。 字元线(Word Line)连接到闸极 , 位元线(Bit Line)则连接到源极 。

4F2 VG 将传统 DRAM 中的平面栅极结构调整为垂直方向 , 可最大限度减少单一数据存储单元的面积占用 , 同时有助于实现高集成度、高速度和低功耗 。

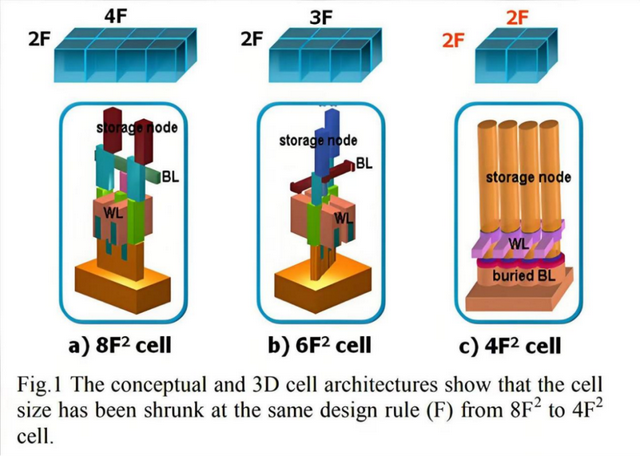

那么4F2是如何由来的呢?是否存在6F2和8F2?是的 。

8F2 :如上图所示 , 早期DRAM采用8F2 RCAT结构 , 位线跨4格 , 字线跨2格 , 总面积8F2(F为最小特征尺寸) , 但源极无法直接与字线连接 , 需留白 , 单元实际占4格位线宽度 。 虽结构简单 , 位线与字线留白却限制存储密度提升 。

6F2 :自130纳米及以下制程起 , 6F2 BCAT结构登场 , 单元布局优化为位线3格、字线2格 , 大幅提升单元密度 。 然而 , 随线路宽度缩小到10纳米级 , 物理极限致电流泄漏、信号干扰频发 , 平面棋盘格排列单元难以为继 。

4F2:为高效利用有限面积 , 竖起水平排列单元或垂直堆叠单元阵列成必然选择 。 4F2结构将源极、栅极、漏极转为垂直结构 , 下层源极接位线 , 其上栅极连字线 , 再往上堆叠漏极与电容器 , 减少电气干扰 , 面积缩小约30% 。

不过4F2结构的内存芯片早在10多年前就有研发了 , 刚进入DDR3时代就有厂商计划使用 , 只是一直没有取得实际的进展 , 制造难度也非常大 。

02三星 , 也紧盯4F2 DRAM

盯上4F2 DRAM的 , 可不只是SK海力士 。

早在2023年 , 三星就组建了一个开发团队 , 目的是进一步推进4F2结构DRAM的应用 , 并将其量产应用于10纳米以下的DRAM制程 。

三星电子表示 , 多家公司正致力于将技术过渡至4F2 垂直通道晶体管 DRAM , 但需要克服一些技术上的挑战 , 包括开发氧化物通道材料和铁电体等新材料 。 业内人士认为 , 三星计划 2025 年即将推出的 4F2 DRAM 的首批样品可能仅仅是内部发布试制样品 。 半导体设备制造商东京电子则估计 , 采用 VCT 和 4F2 技术的 DRAM 将在 2027 年至 2028 年间问世 。

相较于在DRAM单元结构上向z方向发展的VCT DRAM , 三星电子还聚焦在VS-CAT(Vertical Stacked-Cell Array Transistor , 垂直堆叠单元阵列晶体管)DRAM上 , 该技术类似3D NAND一样堆叠多层DRAM 。

除通过堆叠提升容量外 , VS-CAT DRAM 还能降低电流干扰 。 三星电子预计其将采用存储单元和外围逻辑单元分离的双晶圆结构 , 因为延续传统的单晶圆设计会带来严重的面积开销 。

在分别完成存储单元晶圆和逻辑单元晶圆的生产后 , 需要进行晶圆对晶圆(W2W)混合键合 , 才能得到 VS-CAT DRAM成品 。

据悉 , 目前三星电子已在内部实现了16层堆叠的VS-CAT DRAM 。

03有了HBM , 就足够了?

读到这里 , 可能有读者会问:HBM 不也是 3D DRAM 吗?用HBM不就够了吗?为什么还要研究3D?答案是单单依赖HBM , 还存在不足 。

最直观的两点:1、HBM产量不足 。 2、HBM成本过高 。

通往3D DRAM , 主要有这样两条路径 , HBM采用的是最直接的方法 , 垂直堆叠多个 DRAM 芯片 , 并使用硅通孔(TSV)技术垂直连接各层芯片 , 各层 DRAM 通过微凸点与逻辑芯片相连 。

常见的HBM芯片为4和8高以及16高 , 与基本 DRAM 相比 , 这是一种更昂贵的方法 , 因为在封装中堆叠die需要付出努力 , 但对于需要大量附近内存的应用程序 , 如AI , 这是值得的 。

另一种方式是单片堆叠 DRAM , 将多个 DRAM 芯片堆叠在一起 , 但连接方式可能有所不同 。 部分单片堆叠技术采用混合键合技术 , 两个晶圆的金属键合焊盘以及相邻介电材料直接连接 , 这种方式下没有 HBM 结构中芯片之间的导电凸块 , 且存储器芯片厚度更薄 , 堆叠高度整体降低 。

作为一种自然延伸 , 单片堆叠芯片只需少量额外步骤 , 自然这少量的额外步骤也会导致很多困难 。

043D DRAM , 2030年见分晓

有机构预测 , 到2030 年 , 全球 3D DRAM 市场规模有望增长到 1000 亿美元 。

正是看到了这样的发展前景 , 以存储芯片三巨头为代表的厂商都在发力 , 进行相关技术和产品的研发 。 其中三星对该技术最为关注的 , 投入也最大 。

三星通过VCT技术将晶体管垂直排列 , 使单元面积缩小30% , 并结合铪锆氧化物(HZO)材料优化电荷存储性能 。 目前其已成功研发128Gb容量的3D X-DRAM样品 , 目标2030年前将单颗芯片容量扩展至1Tb 。

据悉 , 三星电子在美国硅谷开设了一个新的研发实验室 , 主要进行3D DRAM 研发 。 据悉 , 该实验室隶属于硅谷的 Device Solutions America (DSA) 部门 , 负责监督三星电子在美国的半导体生产 , 并专注于新一代 DRAM 产品的开发 。

除了要在2025 年量产 , 三星电子还要在 2027~2028 年将相关制程节点缩小到 8nm~9nm , 目前 , 最先进的 DRAM 制程约为 12nm 。

SK海力士去年在“VLSI 2024”大会上展示了5层堆叠3D DRAM原型 , 并宣布实现了56.1%的良率 。

其研究论文 , 指出实验中的3D DRAM显示出与目前使用的2D DRAM相似的特性 , 这是海力士首次披露其3D DRAM开发的具体数据和运行特性 。 此外 , 海力士还在研究将IGZO材料应用于3D DRAM , 以解决带宽和延迟方面的挑战 。 IGZO是由铟、镓、氧化锌组成的金属氧化物材料 , 大致分为非晶质IGZO和晶化IGZO 。

美光在2019年就开始了3D DRAM的研究工作 。 截止2022年8月 , 美光已获得了30多项3D DRAM专利 。 相比之下 , 美光专利数量是三星和SK海力士这两家韩国芯片制造商的两三倍 。 美光于 2023 年末在 IEEE IEDM 会议上披露了其 32Gb 3D NVDRAM(非易失性 DRAM)研发成果 。 不过根据外媒 Blocks & Files 从两位受采访的行业分析师处得到的消息 , 这一突破性的新型内存基本不可能走向商业化量产道路 , 但其展现的技术进展有望出现在未来内存产品之中 。

除了大厂 , 有些创业公司也在进行3D DRAM 开发 。

例如 , 美国公司NEO Semiconductor 推出了一种名为 3D X-DRAM 的技术 , 旨在克服 DRAM 的容量限制 。 3D X-DRAM 的单元阵列结构类似于 3D NAND Flash , 采用了 FBC 技术 , 它可以通过添加层掩模形成垂直结构 , 从而实现高良率、低成本和显著的密度提升 。

据NEO 介绍 , 3D X-DRAM 技术可以跨 230 层实现 128Gb 的密度 , 是当前 DRAM 密度的 8 倍 。 NEO 提出了每 10 年容量增加 8 倍的目标 , 计划在 2030~2035 年实现 1Tb 的容量 , 比目前 DRAM 的容量增加 64 倍 。

想要获取半导体产业的前沿洞见、技术速递、趋势解析 , 关注我们!

推荐阅读

- 一粒「扣子」,开启了Agent的全生命周期进化

- 人工智能的最佳DRAM

- LeCun世界模型出2代了,62小时搞定机器人训练,开启物理推理新时代

- 谷歌流量急坠归0?核心员工被「自愿离职」,30年搜索帝国崩塌

- VC均热板加持,独显14英寸全能本七彩虹源N14开启预约

- HarmonyOS 5.1将于7月开启升级!为你的设备注入全新升级体验!

- 6月12日京东618电竞惊喜日开启 买键鼠享三重补贴至高优惠50%

- 32周年:奥拓电子如何以AI+视讯,开启LED光显新纪元

- 荣耀开启“清仓模式”,从3999元跌至2379元,高配版已沦为中端机

- 负责人开启“微博办公”模式,小米下决心重整可穿戴产品线